Bachelor Thesis: Extended Abstract

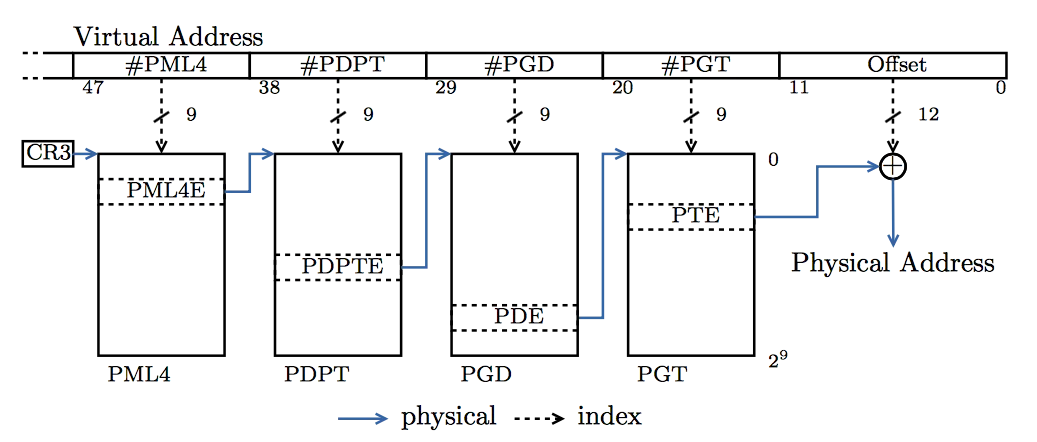

Bachelor Thesis: Extended Abstract Almost fourteen months ago, I started working on my bachelor thesis. Although I finished it half a year ago, it’s still part of my work as a student research assistant. Figure 1b: Page table walk in the x86 64 longmode: With self-reference. Figure 2: Similar flags across all paging levels. Table 1: Virtual addresses of self-mapped tables. During my initial work, most of the code was written for an internal research kernel. I’m now happy that we were able to port it to an open source kernel called eduOS : /RWTH-OS/eduOS ). This minimal operating system is used for practical demo’s and assignments during the OS course at my university. There’s much more I could write about. So this will probably be another separate blog post. The motive for this article is an abstract I wrote for the student research competition of the ASPLOS conference which is held this year in Istanbul, Turkey. Unfortunately my submission got rejected. But as a nice side-effect, I’ve now the chance to present my work to an English audience as well: Download: Extended Abstract (PDF) Self-referencing Page Tables for the x86-Architecture Section titled “Self-referencing Page Tables for the x86-Architecture” A simple Paging Implementation for a minimalistic Operating System Section titled “A simple Paging Implementation for a minimalistic Operating System” Academic advisor: Dr. rer nat. Stefan Lankes Institute for Automation of Complex Power Systems E.ON Energy Research Center, RWTH Aachen University Mathieustr. 10, 52074 Aachen, Germany This was a submission for ASPLOS Student Research Competition ’15 Istanbul, Turkey 1 . Abstract Section titled “Abstract” The adoption of 64 bit architectures went along with an extension of the virtual address space (VAS). To cope with this growth, the memory management unit (MMU) had to be extended as well. For paging-based systems like Intel’s x86-architecture this was realized by adding more levels of indirection to the page table walk. This walk translates virtual pages to physical page frames (PF) by performing look-ups in a radix / prefix tree in which every node represents a page table ( Figure 1a ). Since the tables are part of the translation process, they must be referenced by physical page frame numbers (PFN, blue line). As the operating system is only eligible to access the VAS, it cannot follow the path of a walk. In order to allow the manipulation of page tables, it must provide: Access to the table entries, by mapping the tables themselves to the VAS. A mapping between physical references to corresponding locations in the VAS. Additionally, every level of the page table walk increases the complexity of managing these mappings. They also increase the memory consumption by occupying physical page frames. It is possible to avoid both drawbacks by the technique described in the following. In my bachelor thesis, I presented an approach, which is compatible with both the 32 bit and 64 bit version of Intel’s x86-architecture. This allows for a replacement of two code bases, one for each architecture, by...

Preview: ~500 words

Continue reading at Hacker News

Read Full Article